# 54LS/74LS323 010<sup>150</sup>

### 8-BIT UNIVERSAL SHIFT/STORAGE REGISTER

(With Synchronous Reset and Common I/O Pins)

**DESCRIPTION** — The '323 is an 8-bit universal shift/storage register with 3-state outputs. Its function is similar to the '299 with the exception of Synchronous Reset. Parallel load inputs and flip-flop outputs are multiplexed to minimize pin count. Separate inputs and outputs are provided for flip-flops Qo and Qr to allow easy cascading. Four operation modes are possible: hold (store), shift left, shift right, and parallel load. All modes are activated on the LOW-to-HIGH transition of the Clock.

- COMMON I/O FOR REDUCED PIN COUNT

- FOUR OPERATION MODES: SHIFT LEFT, SHIFT RIGHT, PARALLEL LOAD AND STORE

- SEPARATE CONTINUOUS INPUTS AND OUTPUTS FROM QQ AND Q7

ALLOW EASY CASCADING

- FULLY SYNCHRONOUS RESET

- 3-STATE OUTPUTS FOR BUS ORIENTED APPLICATIONS

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                        | MILITARY GRADE                                                                                          | PKG  |

|--------------------|-----|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V} \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C} \text{ to } +125^{\circ} \text{ C}$ | TYPE |

| Plastic<br>DIP (P) | Α   | 74LS323PC                                                                               |                                                                                                         | 9Z   |

| Ceramic<br>DIP (D) | A   | 74LS323DC                                                                               | 54LS323DM                                                                                               | 4E   |

| Flapak<br>(F)      | Α   | 74LS323FC                                                                               | 54LS323FM                                                                                               | 4F   |

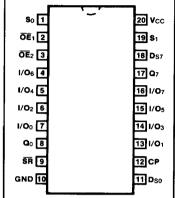

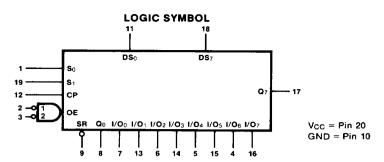

# CONNECTION DIAGRAM PINOUT A

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                          | DESCRIPTION                               | <b>54/74LS (U.L.)</b><br>HIGH/LOW |  |

|------------------------------------|-------------------------------------------|-----------------------------------|--|

| CP                                 | Clock Pulse Input (Active Rising Edge)    | 0.5/0.25                          |  |

| D <sub>S0</sub>                    | Serial Data Input for Right Shift         | 0.5/0.25                          |  |

| Ds7                                | Serial Data Input for Left Shift          | 0.5/0.25                          |  |

| So, S1<br>SR<br>OE1, OE2           | Mode Select Inputs                        | 1.0/0.50                          |  |

| SR                                 | Synchronous Reset Input (Active LOW)      | 0.5/0.25                          |  |

| OE <sub>1</sub> , OE <sub>2</sub>  | 3-State Output Enable Inputs (Active LOW) | 0.5/0.25                          |  |

| /O <sub>0</sub> — I/O <sub>7</sub> | Parallel Data Inputs or                   | 1.0/0.50                          |  |

|                                    | 3-State Parallel Outputs                  | 65/15                             |  |

|                                    |                                           | (25)/(7.5)                        |  |

| Q <sub>0</sub> , Q <sub>7</sub>    | Serial Outputs                            | 10/5.0                            |  |

|                                    |                                           | (2.5)                             |  |

**FUNCTIONAL DESCRIPTION** — The '323 contains eight edge-triggered D-type flip-flops and the interstage logic necessary to perform synchronous reset, shift left, shift right, parallel load and hold operations. The type of operation is determined by  $S_0$  and  $S_1$  as shown in the Mode Select Table. All flip-flop outputs are brought out through 3-state buffers to separate I/O pins that also serve as data inputs in the parallel load mode.  $Q_0$  and  $Q_7$  are also brought out on other pins for expansion in serial shifting of longer words.

A LOW signal on  $\overline{SR}$  overrides the Select inputs and allows the flip-flops to be reset by the next rising edge of CP. All other state changes are also initiated by the LOW-to-HIGH CP transition. Inputs can change when the clock is in either state provided only that the recommended setup and hold times, relative to the rising edge of CP, are observed.

A HIGH signal on either  $\overline{OE}_1$  or  $\overline{OE}_2$  disables the 3-state buffers and puts the I/O pins in the high impedance state. In this condition the shift, load, hold and reset operations can still occur. The 3-state buffers are also disabled by HIGH signals on both  $S_0$  and  $S_1$  in preparation for a parallel load operation.

#### **MODE SELECT TABLE**

| INPUTS      |       |       |       | RESPONSE                                                                                                                                                                   |  |  |

|-------------|-------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SR S₁ S₀ CP |       | СР    |       |                                                                                                                                                                            |  |  |

| LHHH        | XIJII | XIIJI | ×4444 | Synchronous Reset; $Q_0 - Q_7 = LOW$ Parallel Load; $I/O_n - Q_n$<br>Shift Right; $D_{S0} - Q_0$ , $Q_0 - Q_1$ , etc. Shift Left; $D_{S7} - Q_7$ , $Q_7 - Q_6$ , etc. Hold |  |  |

H = HIGH Voltage Level L = LOW Voltage Level

X = Immaterial

#

|                         |           |             | DAMOE /    | and the second of the second of the second |

|-------------------------|-----------|-------------|------------|--------------------------------------------|

| DC CHARACTERISTICS OVER | OPERATING | TEMPERATURE | HANGE UNIC | ess otherwise specified)                   |

| SYMBOL | PARAMETER            | 54/74LS |     | UNITS | CONDITIONS                                 |

|--------|----------------------|---------|-----|-------|--------------------------------------------|

|        | ranameten            | Min     | Max |       |                                            |

| lcc    | Power Supply Current |         | 60  | mA    | V <sub>CC</sub> = Max,<br>Outputs Disabled |

# AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{ C}$ (See Section 3 for waveforms and load configurations)

|                  |                                                             | <b>54/74LS</b> C <sub>L</sub> = 15 pF |          | UNITS | CONDITIONS                                                                |

|------------------|-------------------------------------------------------------|---------------------------------------|----------|-------|---------------------------------------------------------------------------|

|                  | PARAMETER                                                   |                                       |          |       |                                                                           |

|                  |                                                             | Min                                   | Max      |       |                                                                           |

| f <sub>max</sub> | Maximum Input Frequency                                     | 35                                    |          | MHz   | Figs. 3-1, 3-8                                                            |

| tPLH<br>tPHL     | Propagation Delay<br>CP to Q <sub>0</sub> or Q <sub>7</sub> |                                       | 23<br>25 | ns    | Figs. 3-1, 3-8                                                            |

| tplH<br>tpHL     | Propagation Delay<br>CP to I/On                             |                                       | 25<br>29 | ns    |                                                                           |

| tpzh<br>tpzL     | Output Enable Time                                          |                                       | 18<br>23 | ns    | Figs. 3-3, 3-11, 3-12<br>R <sub>L</sub> = 2 k $\Omega$                    |

| tpHZ<br>tpLZ     | Output Disable Time                                         |                                       | 15<br>15 | ns    | Figs. 3-3, 3-11, 3-12<br>$R_L = 2 \text{ k}\Omega$ , $C_L = 5 \text{ pF}$ |

# AC OPERATING REQUIREMENTS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ} \text{ C}$

| SYMBOL                                   | PARAMETER                                                       | 54/74LS  |     | UNITS | CONDITIONS |  |

|------------------------------------------|-----------------------------------------------------------------|----------|-----|-------|------------|--|

|                                          |                                                                 | Min      | Max | ]     | 0051710.00 |  |

| ts (H)<br>ts (L)                         | Setup Time HIGH or LOW<br>So or S1 to CP                        | 24<br>24 |     | ns    | Fig. 3-6   |  |

| th (H)<br>th (L)                         | Hold Time HIGH or LOW<br>S <sub>0</sub> or S <sub>1</sub> to CP | 0<br>0   |     | ns    |            |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW I/On, Dso, Ds7 to CP                     | 10<br>10 |     | ns    | Fig. 3-6   |  |

| th (H)<br>th (L)                         | Hold Time HIGH or LOW I/On, Dso, Ds7 to CP                      | 0<br>0   |     | ns    |            |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>SR to CP                              | 15<br>15 |     | ns    | Fig. 3-6   |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>SR to CP                               | 0<br>0   |     | ns    |            |  |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CP Pulse Width HIGH or LOW                                      | 15<br>15 |     | ns    | Fig. 3-8   |  |