# FM/IF system

The BA4110 IC is an FM detector and intermediate frequency (IF) (10.7 MHz) amplifier.

Almost all necessary functions, such as FM tuner, signal-level meter output, AGC output, and AFC output, are built into the BA4110. Soft muting, a feature for freely setting the noise-suppression on the output, makes this IC suitable for a wide-band FM-IF system.

Compared with conventional products, the packaging is much smaller allowing compact receivers to be built.

### **Features**

- · available in a ZIP16 package

- wide operating voltage range (6 V ~ 12 V)

- low distortion

- good signal-to-noise ratio and high sensitivity

- built in features for suppression of white noise when receiving weak signals, between stations, and when not tuned accurately

- variable muting to allow maximum audio attenuation. Muting slope is tied to input signal level

- signal strength meter output is provided that can be used as a control signal for the BA1350 multiplexer

- AFC output

- AGC output to provide control of the front end receiver

- small and compact, requiring few external components

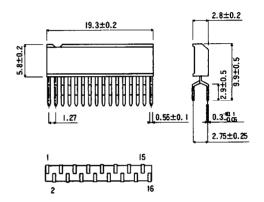

## **Dimensions (Units:mm)**

#### **BA4110 (ZIP16)**

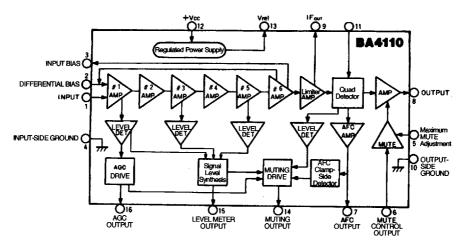

#### **Functions**

- FM IF amplifier and limiter

- · quadrature detector

- · AFC and tuning meter output

- AGC output

- · signal level meter output

- muting for weak signal reception

- · muting for detuned conditions

# **Applications**

- FM car stereos

- consumer stereo systems

- music centers

# **Block diagram**

# Absolute maximum ratings ( $T_a = 25$ °C)

| Parameter             | Symbol           | Limits                   | Unit |  |

|-----------------------|------------------|--------------------------|------|--|

| Power supply voltage  | V <sub>CC</sub>  | 14                       |      |  |

| Power dissipation     | P <sub>d</sub>   | 500                      | mW   |  |

| Operating temperature | T <sub>opr</sub> | <b>−25</b> ~ <b>+75</b>  | °C   |  |

| Storage temperature   | T <sub>stg</sub> | <b>−55</b> ~ <b>+150</b> | °C   |  |

# Electrical characteristics ( $T_a = 25$ °C, $V_{CC} = 9 V$ )

| Parameter                 | Symbol           | Min | Typical | Max | Unit              | Conditions                                                        |

|---------------------------|------------------|-----|---------|-----|-------------------|-------------------------------------------------------------------|

| Operating voltage         | V <sub>CC</sub>  | 6   | 9       | 12  | V <sub>dc</sub>   |                                                                   |

| Quiescent current         | I <sub>Q</sub>   | 10  | 22      | 37  | mA                | No output                                                         |

| Limiting sensitivity      | V <sub>IN</sub>  |     | 25      | 34  | dΒμV              | at - 3 dB                                                         |

| Detector output           | V <sub>OUT</sub> | 320 | 380     | 440 | mV <sub>rms</sub> | 100% modulation, f = 1 kHz,<br>V <sub>IN</sub> = $100$ dB $\mu$ V |

| Total harmonic distortion | THD              |     | 0.2     | 1.2 | %                 | 100% modulation, f = 1 kHz,<br>V <sub>IN</sub> = $100$ dB $\mu$ V |

| Signal-to-noise ratio     | S/N              | 65  | 80      |     | dB                | 100% modulation, $V_{IN} = 100 \text{ dB}\mu\text{V}$             |

| AM suppression level      | AMR              | 45  | 60      |     | dB                |                                                                   |

| Output impedance          | Z <sub>OUT</sub> | 2.8 | 3.9     | 5.0 | kΩ                |                                                                   |

Note: For the test circuit, see Figure 15.

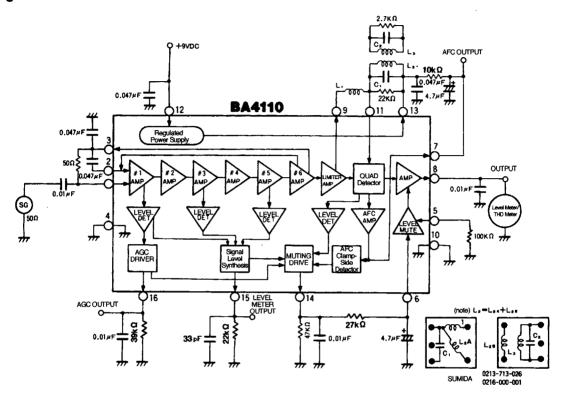

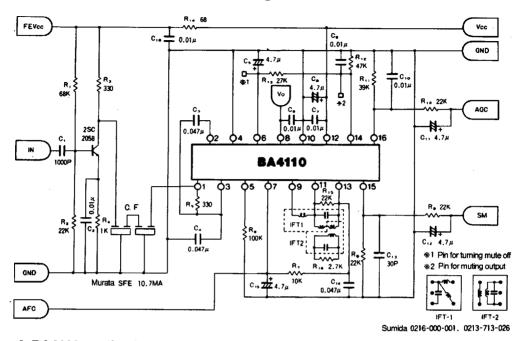

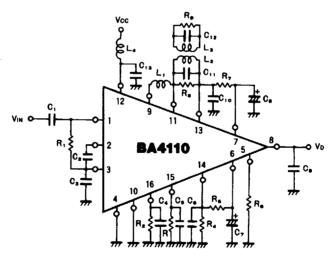

Figure 1 Test circuit

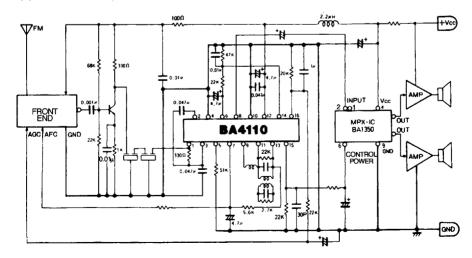

Figure 2 Application example

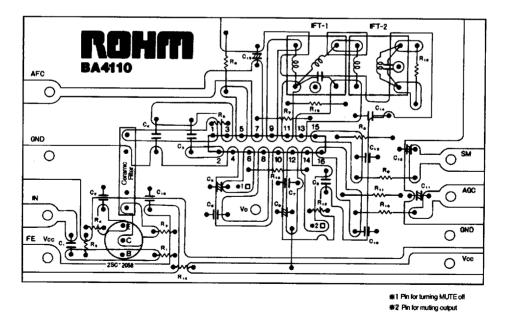

Figure 3 BA4110 application circuit board diagram

Figure 4 BA4110 application circuit board diagram (solder side)

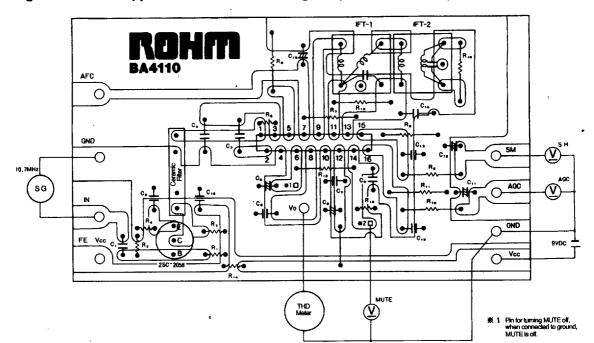

Figure 5 BA4110 application circuit board diagram (test connections)

# **Circuit operation**

# Integrated circuit

# IF amplifier

The IF amplifier consists of a six-stage differential amplifier.

Amplifier gain is approximately 80 dB. Output passes through the emitter follower and signals are sent to the quadrature limiter amplifier. The feedback bias is returned to the IF amplifier input.

The input bias voltage is normally 2.6 V.

# Quadrature limiter amplifier

This amplifier outputs the carrier signal from the IF amplifier to the quadrature detector, extracts carrier signals for phase shifting, and outputs them on pin 9. The amplifier gain is approximately 10 dB from the pin 9 IF output to the IF amplifier output. The output impedance of pin 9 is approximately 400  $\Omega$ .

#### **Quadrature detector**

The quadrature detector consists of a double-balanced differential amplifier that detects the proper phase-carrier signal voltage from the limiter amplifier by switching according to a carrier signal that is shifted 90° through an external phase-shifting device between pin 9 and pin 11.

Usually the quad signal-input pin (pin 11) is biased to approximately 4.8 V, about the same as pin 13 ( $V_{ref}$ ), due to the external tuning coil.

## **Muting operational amplifier**

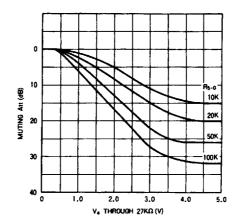

Soft-audio muting of the audio signal from the quadrature detection circuit is performed in the double-balanced differential-type electronic volume control. The muting characteristic is controlled by the resistance between pin 5 and ground and the pin 6 inflow current (See Figure 6).

Pin 5 is set internally to approximately 2.1 V when pin 5 is open. The operating voltage of the pin 8 detector output is set to approximately 4.8 V at the time of coil tuning—about the same voltage as pin 13 ( $V_{ref}$ ). The output impedance ( $R_L$ ) is approximately 4 k $\Omega$ . The post-amplifier gain is approximately 30 dB.

Figure 6 Muting control voltage to mute attenuation

# Signal level detector

This detector directs the IF amplifier output in the first, third, and fifth stages of the six-stage IF amplifier structure at each emitter follower. It discerns the level by detecting the peak IF-carrier signal, synthesizes this with the level-detection current, and outputs the result.

The level meter output (pin 15) is the emitter follower output, and the maximum level output (for the strongest received signal) is set internally to clamp at approximately 5.3 V.

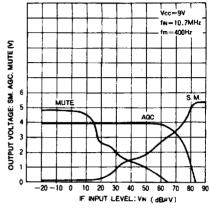

### **AGC** output circuit

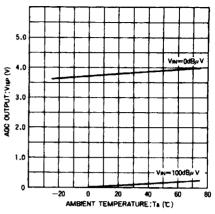

This circuit detects the signal strength from the stage 1 amplifier and lowers the voltage on pin 16 in relation to the detected strength. Pin 16 is usually set to 3.8 V for the weakest signal.

## **AFC** output circuit

The circuit configuration for the AFC amplifier output is the same as that for the detector output. Because the load can be changed by the value of the resistor connected between pin 7 and pin 13, it is possible to set the AFC sensitivity and the mute range.

When tuned, the pin 7 dc voltage is 4.8 V, almost the same as  $V_{ref}$  on pin 13. When detuned, the circuit is configured internally to clamp at  $(V_{TUNED} \pm V_F)$ .

When the pin 7 dc voltage is clamped at  $V_F$ , it raises pin 14 mute output to approximately 4.7 V by using a side detection circuit.

### internal regulated power supply

The internal regulated power supply consists of a constant current circuit and a low-voltage zener diode. The IC operates normally for input voltages as low as 6 V. (Pin 12 is the power input pin  $(V_{CC})$ .)

## External components (See Figures 2 and 7)

### Figure 7 External components

C<sub>1</sub>: Input coupling capacitor R<sub>1</sub>: IF amplifier input resistance

The input impedance of the IF amplifier is determined by this resistor. The resistance value must be set to match the output impedance of the previous stage. Use a 330 k $\Omega$  resistor if a ceramic filter is connected to the previous stage.

C<sub>1</sub>, C<sub>3</sub>: IF amplifier bypass capacitor: In the feedback bias of the self-biasing IF amplifier, this capacitor bypasses the IF carrier signal (and other high-frequency signal elements) from the IF amplifier output to ground. As the value of the capacitor is decreased, the operation of the IF amplifier becomes unstable. A capacitor with good high-frequency characteristics must be used.

**R<sub>2</sub>: AGC output load resistance**: The AGC output voltage on pin 16 and this resistance value are used to set the muting signal level for the weakest input.

For example, as the resistance of  $R_2$  is decreased, the current between pin 16 and the ground increases. Due to this increase, pin 14 muting output current increases proportionally and the audio output is further suppressed. (See Figure 28).

Therefore, it is also possible to set the input-limiting sensitivity when soft muting is executed, using the  $R_2$  resistor that is connected between pin 16 and ground. A change in the resistance of  $R_2$  produces a variation of less than 10 mV in the AGC output voltage and the output characteristic as measured against the AGC input. This allows the resistor  $R_2$  to be tuned for the best mute level with little impact on the AGC.

$C_4$ : Capacitor for smoothing AGC voltage: When  $C_4$  is not connected, an alternating IF carrier frequency current remains on the pin in order for the AGC output to extract the IF carrier signal from the first stage IF amplifier with the level detection circuit.

Therefore, if this capacitor is too small, the IC may malfunction because an alternating current will be returned to the front end rather than being bypassed to ground.

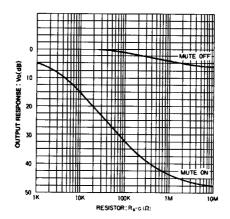

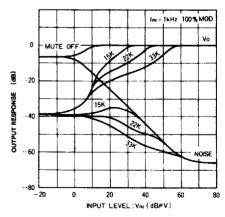

**R<sub>3</sub>: Signal level meter output load resistance**: This resistor is used to set the relationship between the input signal level and the muting attenuation.

For example, when the value of this resistor is small, the gradient of the input signal level for the current between pin 15 and ground increases. This is equivalent to the signal level meter output voltage.

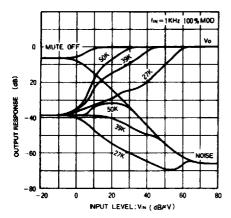

Since the input gradient of the current, which reduces pin 14 muting output, also increases, the audio suppression against the input signal level gradient also becomes steeper (see Figure 27).

As the value of this resistance is changed, the signal level meter output barely changes and remains stable so the muting characteristic can be adjusted independently. Using the signal level meter output, a parallel resistor can be added between pin 15 and ground when using a multiplexer in the following stage and when driving the level meter. You must select a comparatively large resistance value compared to the resistor that has been adjusted for a single IC unit.

C<sub>5</sub>: Capacitor for smoothing level meter output voltage: This capacitor attenuates both the alternating current of the IF carrier signal which remains in the level detection circuit output and other high frequency signals. When this value is large, a harmonic wave in pin 14 muting output increases as the muting output rises, and the input response time of the signal level meter output also becomes greater.

$R_4$ : Muting output load resistance: This is the load resistance for the muting output. When this value is too large, it takes time to eliminate muting and when the value is too small, the quiescent current increases. The recommended value is 47 k $\Omega$ .

C<sub>6</sub>: Capacitor for smoothing muting output: This capacitor bypasses the high-frequency noise element, which is included in the muting output, to ground. Because the mute output is through the post amplifier, any high frequency signal allowed to stay in the muting output can cause the S/N ratio to deteriorate and breaks in audio may occur with a "pop-like" noise.

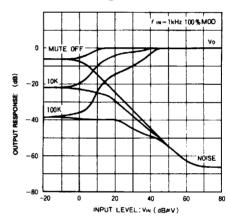

**R<sub>5</sub>: Muting drive current adjustment resistor**: This resistor is connected between the muting output (pin 14) and the post amplifier input (pin 6). It controls the pin 6 input current, which controls the post amplifier input sensitivity with respect to the muting output voltage.

By changing this resistance, it is possible to change the gradient of the input signal level to the amount of muting attenuation.

If this resistance is decreased, pin 6 input current increases, and audio output suppression increases. This means that the gradient that controls the relationship between the input signal level and the amount of muting attenuation increases.

Take care when determining this resistor value. If it is made too large, then even when the pin 14 muting output increases to its maximum value, the maximum muting attenuation set by the resistor between pin 5 and the ground cannot be obtained (see Figure 26).

**C<sub>7</sub>: Muting bypass capacitor:** Together with R<sub>5</sub>, this capacitor forms the low pass filter (LPF) and bypasses the ac elements from the post amplifier to ground.

When this value is small, the ac element remains on pin 6, and as the audio signal is modulated through the post amplifier, beat interference occurs.

If this capacitor is made too large, the time for eliminating muting lengthens.

**R<sub>6</sub>: Muting maximum attenuation adjustment resistor**: The maximum mute attenuation is set by this resistor. This occurs when there is no signal (quiescent) or when the signal is detuned.

As the value of this resistor is decreased, pin 5 current increases. This lowers the standard bias level of the post amplifier. In turn, the signal bias is increased relatively and the post amplifier gain becomes larger. Therefore, the maximum mute attenuation becomes smaller. (See Figures 2, 6, and 8).

Figure 8 Setting resistor R<sub>5</sub>

${

m C_8:}$  Capacitor for de-emphasis: Since the pin 8 output impedance is approximately 3.9 k $\Omega$ , the time constant of de-emphasis is determined by the value of  ${

m C_8.}$  If a stereo multiplexer is used as the next stage, it is connected by this constant. Sufficient stereo separation cannot be obtained (due to signal phase deviation) if  ${

m C_8}$  remains in the circuit. In this case,  ${

m C_8}$  must either be removed or a much smaller value must be selected so that stereo separation can be obtained.

**C<sub>9</sub>: Capacitor for smoothing AFC output:** This capacitor bypasses the detection signal (which is output from pin 7) to ground. The recommended value is  $4.7 \mu F$ .

If the AFC is returned to the front end device, any residual ac component in this signal modulates the frequency of the front end local oscillator signal. This causes erroneous operation similar to a strong electric field.

Furthermore, when there is a residual audio signal, the side detection circuit may also operate erroneously. In this case, because the muting works regardless of tuning, a normal detection output level cannot be obtained.

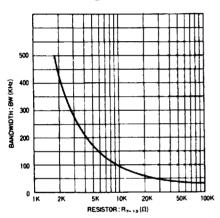

**R<sub>7</sub>: Muting range adjustment resistance:** This resistor is connected between pin 7 and pin 13. It allows adjustment of the muting range and AFC sensitivity. As the value of the resistor is made smaller, the muting range widens and the AFC sensitivity decreases (See Figure 9).

Figure 9 Relationship between shunt resistor AFC output

C<sub>10</sub>: Internal regulator bypass capacitor R<sub>8</sub>: Shunt resistor

R<sub>8</sub> is used to shunt the impedance of the Side 1 LC parallel resonance circuit of the IFT.

When this value is small, the Q-value of the resonance circuit becomes smaller so the gain drops. This expands the deviation range and linearity but decreases the recovered audio and sensitivity. When the muting resistance is too small, the gain drops, even when the input signal is strong, and the dc voltage on pin 14 (mute output) rises due to a decrease in the pin 11 quad signal level. This suppresses the audio output.

50ΚΩ 10ΚΩ

CARRIER FREQUENCY: In (MHz)

3.9KΩ

**R<sub>9</sub>: Shunt resistor:** This resistance shunts the impedance characteristic in the side 2 LC parallel resonance circuit of the IFT. Because the impedance of the side 2 coil shows the opposite characteristic of the 1st coil to the frequency, each has its own optimum value.

Inductances L<sub>2</sub> and L<sub>3</sub>, Capacitors C<sub>11</sub>, C<sub>12</sub>: IFT: Distortion in the detection output and detection output voltage are almost completely determined by the Q-value of the quadrature detection coil. When the Q-value of the coil is enlarged, the detection output voltage becomes larger; however, the minimum distortion value and the range characteristic both deteriorate.

Therefore, set the Q-value according to the shunt resistance, which is added linearly.

**L<sub>1</sub>: Phase-shift inductor:** The input to this device is the IF carrier signal (pin 9) and it outputs the carrier phase shifted by 90° to the quadrature detector circuit as the quad. Because it extracts the carrier signal directly from the IF amplifier output, the signal line should be shielded if the IF amplifier is unstable.

C<sub>13</sub>: Power supply bypass capacitor L<sub>4</sub>: Power supply choke coil

## Adjustment of the circuit

**Power supply**: The supply voltage (on pin 12) can be in the range between  $6 \sim 12$  V. Because the internal regulator operates as low as 6 V, dc operation of the IC is stable for voltages as low as 6 V. For the RF signal, however, the S-curve of the detection output becomes clipped in the vicinity of  $6.5 \sim 7.0$ V. Therefore, for power supply voltages in this range or less, stable operation of the detection output range cannot always be obtained.

**Detection output level:** When an external constant is used as shown in the application circuit, the detection output level can be made as high as 300 mV (at 100% modulation) by adjusting the IFT coil.

The detection output level changes depending on the value of the shunt resistor of the first IFT coil and by the value of the maximum muting attenuation resistor between pin 5 and ground.

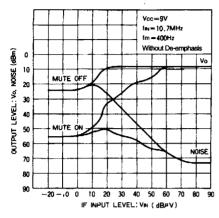

**Noise:** The signal-to-noise ratio during normal operation is approximately  $80~\mathrm{dB}$  (at 100% modulation). The noise level when the input signal is weak or when the circuit is detuned can be set through soft muting.

**Distortion rate**: By adjusting the pin 11-to-pin 13 tuning coil and selecting the appropriate S-characteristic, a distortion rate of approximately 0.3% (at 100% modulation) for single tuning and approximately 0.1% (at 100% modulation) for multiple tuning is obtained.

**DC output level**: When adjusting the coil so that the detection output level is at its maximum, the dc output level becomes approximately 4.8 V, almost the same pin 13 ( $V_{ref}$ ).

**Input limiting sensor**: It is possible to set the input limiting sensor using the AGC-output load resistor between pin 16 and ground when soft muting is used.

For example, when this resistance is made smaller, the input limiting sensor switches over to the side with the stronger input. When soft muting is not used, it becomes a regular input limiting sensor of normally  $25~\mathrm{dB}\mu\mathrm{V}$  at the IC pin input level.

**AFC**: The AFC range and sensitivity change depending on the IFT coil gain, and the muting range adjustment resistor between pin 7 and pin 13.

The IFT coil gain can be adjusted by the shunt resistor. However, it is easier to first set the detection output level and the distortion rate by the coil gain, and then to adjust the AFC characteristic with the resistor between pin 7 and pin 13. The relationship between the value of the shunt resistor and the AFC output is shown in Figure 9. Care must be taken since the muting range also changes when adjusting the AFC characteristic using this resistor.

When switching the AFC using the ON/OFF switch, set the dc level of the central frequency when the switch is ON and the dc level relating to the FE AFC input pin when the switch is OFF at the same level.

Configure the switch circuit so that the dc level of the  $V_{ref}$  pin when the AFC is OFF connects to the AFC input pin of the front end since the AFC output (pin 7) is set to almost the same potential as the pin 13 ( $V_{ref}$ ) when the input signal is tuned.

Furthermore, if pin 7 is left open when the AFC is OFF, the detection output level, the appropriate frequency for output distortion and the central frequency of the range become out of sync with each other. In this case, configure the circuit so that a load, equal to the input impedance of the FE AFC input pin is connected between pin 7 and ground when the AFC is OFF.

**AGC**: Because the AGC output (pin 16) is voltage driven, the output is almost independent of the external load. The dc output is normally 3.8 V unless the load is excessive. All alternating currents must be removed by a filter when connecting the AGC into the front end.

**Muting**: Muting is configured by using an operational amplifier. The gain is changed by the control current which is generated by the muting output circuit.

The operational amplifier acts like an electronic volume control in which the gain drops as the control current from pin 6 increases. Maximum attenuation is set by the resistor between pin 5 and ground. As shown in Figure 8, the larger the resistance value, the larger the maximum attenuation. Caution must be used when selecting the resistor value since the detection output level is also changed by the same resistor.

When the mute is used, pin 6 is at almost the same potential as  $V_{\text{F}}$ , and the control current is determined by the muting output voltage (pin 14) and the resistance between pin 14 and pin 6. Therefore, as the resistor value is changed, and since the control current value is dependent on the muting output voltage, the gradient of the muting attenuation will change.

For example, if this resistor value is decreased, the gradient becomes steeper. When adjusting the resistor to change the gradient of muting attenuation, be careful not to make the resistance too large, because then, even if the muting output voltage is at its maximum, the maximum muting attenuation will not be obtained.

The muting output voltage synthesizes the muting output at the time of detuning and the muting output when the input is weak by using an OR circuit. The output is on pin 14. When the AFC output during detuning is  $\pm V_F$  or above, the muting output at the time of detuning clamps the AFC output to the standard voltage and detects the  $V_F$  at the same time, raising the muting output up to the standard 4.7 V.

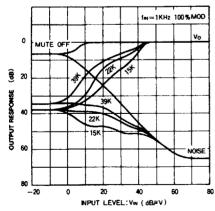

In the same way as the AFC range, the muting range is changed by altering the coil and the resistor value between pin 7 and pin 13. Note that it is easier to set the range using the resistor between pin 7 and pin 13 (See Figure 26).

The muting characteristic, when the input is weak, is set by the AGC output load resistor between pin 16 and ground and by the signal level meter load resistor between pin 15 and ground.

In other words, the muting initiation input level is set by the AGC output load resistance. The gradient of the input signal vs. the amount of muting attenuation is set by the signal level meter load resistance. When the AGC output load resistance value is decreased, the muting initiation input level switches over to the side with the strongest input.

When the value of the signal level meter load resistance is lowered, the gradient of the input signal vs. amount of muting attenuation increases.

Figure 10

Figure 11

#### Precautions for use

### **Adjustment precautions**

**S-characteristic**: When observing the S-characteristic in the detection output, it is not synchronized with the sweep signal, because the quiescent muting effect of the sweep generator is set by a fixed time constant filter between pin 14 and pin 6. Connect pin 6 to ground and turn off the operational amplifier muting function when measuring the S-characteristic in the detection output.

**Power supply filter:** Because a high gain amplifier is built into the BA4110, make sure that the prior amplifier and the FE are not ac coupled through the power supply line. An effective method of isolation is to insert an LC filter into the power supply line. If you use an RC filter, be aware of the drop in voltage that results.

# Printed circuit board wiring precautions

It is very easy to degrade the performance of the BA4110 if the printed circuit board is not arranged correctly.

The ground can be the cause of unwanted oscillation. Similarly the pattern must be made so that the output signal current does not couple with the input section.

High frequency signal lines may not allow favorable distortion rate characteristics to be obtained and a deviation at the point of tuning may occur due to the impedance of the line. To reduce this tendency, make these lead wires and signal lines are as short as possible. Figure 3 shows an example of an application board pattern as a reference.

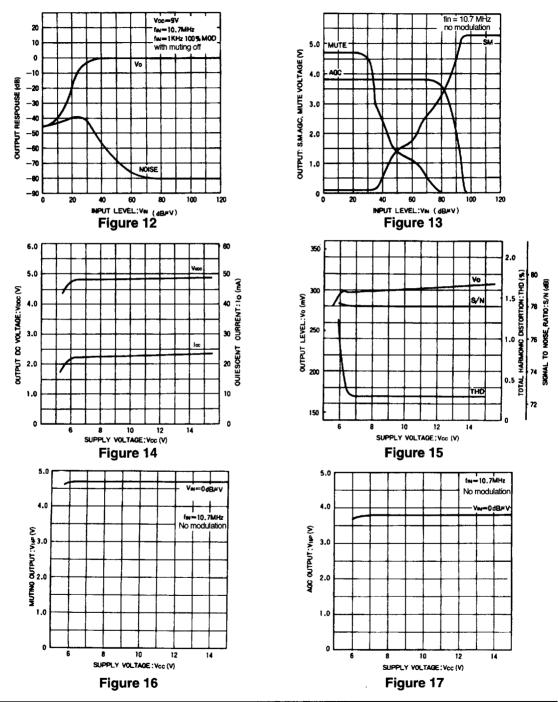

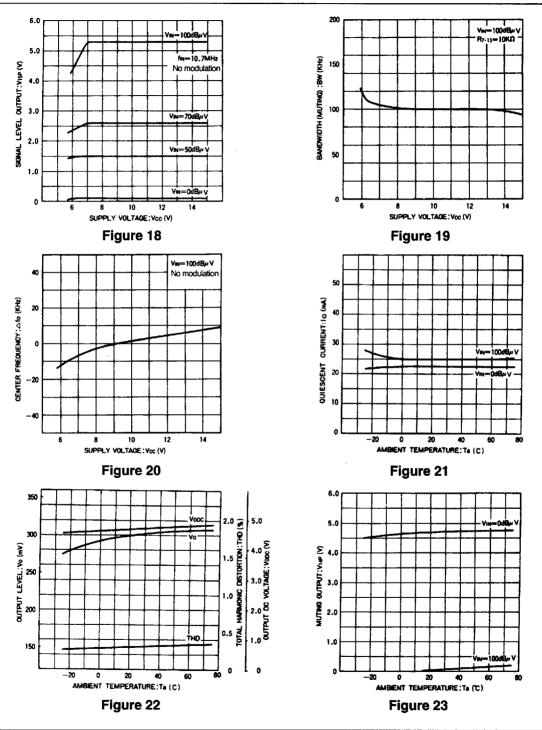

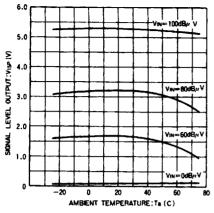

#### **Electrical characteristic curves**

**Audio Integrated Circuits**

Figure 24

Figure 26 Setting resistor R<sub>7</sub>

Figure 28 Setting resistor R<sub>5</sub>

Figure 25

Figure 27 Setting resistor R<sub>6</sub>

Figure 29 Setting resistor on pin 15-GND

Figure 30 Setting resistor R2